I recently added a code coverage option to the VHDL compiler, nvc, I’m working on. I tend to find code coverage a really useful tool when I’m writing RTL, especially the sort of control-dominated designs I do in my day job. I find Modelsim’s HTML coverage reports a bit frustrating so I’m trying to do something more user-friendly in my simulator.

If you elaborate your design with the --cover option the generated code will be annotated to gather the following kinds of coverage:

- Statement – A counter is added for each executable statement in the design. A statement must be executed at least once to be “covered”.

- Branch – A branch is covered if it is both taken and not-taken at least once during execution

- Condition – A condition here is a Boolean sub-expression of branch test and it is covered by evaluating to both TRUE and FALSE at least once. For example

if A and B thencontains one branch but two sub-conditions.

After a run with coverage enabled the statistics are automatically reported:

** Note: coverage report generated in /tmp/work/WORK.TEST.cover/

282/289 statements covered

71/94 branches covered

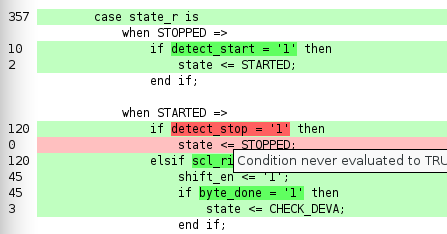

85/108 conditions coveredA HTML report is then generated which contains a top-level summary and a detailed report for each source file:

You can mouse over a non-covered branch or condition to get a hint as to why it was not covered.

The implementation is currently a work-in-progress but functions well enough for light usage. The biggest limitation at the moment is that the report only contains aggregated statistics per-file rather than per-instance statistics.

Posts

Posts

woooOOOO shiny

December 6, 2013 @ 9:16 pm

i want to study how to write test branch in VHDL

April 30, 2014 @ 9:44 am